# **ASM386 Assembly Language Reference**

Order Number: 469165-003

In the United States, additional copies of this manual or other Intel literature may be obtained by writing:

Literature Distribution Center

Intel Corporation

P.O. Box 7641

Mt. Prospect, IL 60056-7641

Or you can call the following toll-free number: 1-800-548-4725

In locations outside the United States, obtain additional copies of Intel documentation by contacting your local Intel sales office. For your convenience, international sales office addresses are printed on the last page of this document. Contact your local sales office to obtain the latest specifications before placing your order.

Intel Corporation (Intel) makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel assumes no responsibility for any errors that may appear in this document. Intel makes no commitment to update nor to keep current the information contained in this document. No part of this document may be copied or reproduced in any form or by any means without prior written consent of Intel. Intel retains the right to make changes to these specifications at any time, without notice.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's Software License Agreement. **U.S. GOVERNMENT RESTRICTED RIGHTS:** These software products and documentation were developed at private expense and are provided with "RESTRICTED RIGHTS." Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR 52.227-14 and DFAR 252.227-7013 et seq. or its successor.

The Intel logo, i960, Pentium, and iRMX are registered trademarks of Intel Corporation, registered in the United States of America and other countries. Above, i287, i386, i387, i486, Intel287, Intel386, Intel387, Intel486, Intel487 and EtherExpress are trademarks of Intel Corporation.

Adaptec is a registered trademark of Adaptec, Inc. AT, IBM and PS/2 are registered trademarks and PC/XT is a trademark of International Business Machines Corporation. All Borland products are trademarks or registered trademarks of Borland International, Inc. CodeView, Microsoft, MS, MS-DOS and XENIX are registered trademarks of Microsoft Corporation. Comtrol is a registered trademark and HOSTESS is a trademark of Comtrol Corporation. DT2806 is a trademark of Data Translation, Inc. Ethernet is a registered trademark of Xerox Corporation. Hayes is a registered trademark of Hayes Microcomputer Products. Hazeltine and Executive 80 are trademarks of Hazeltine Corporation. Hewlett-Packard is a registered trademark of Hewlett-Packard Co. MIX® is a registered trademark of MIX Software, Incorporated. MIX is an acronym for Modular Interface eXtension. MPI is a trademark of Centralp Automatismes (S.A.). NetWare and Novell are registered trademarks of Novell Corp. NFS is a trademark of Sun Microsystems, Inc. Phar Lap is a trademark of Phar Lap Software, Inc. Soft-Scope is a registered trademark of Concurrent Sciences, inc. TeleVideo is a trademark of TeleVideo Systems, Inc. UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company Limited. VAX is a registered trademark and VMS is a trademark of Digital Equipment Corporation. Visual Basic and Visual C++ are trademarks of Microsoft Corporation. All Watcom products are trademarks or registered trademarks of Watcom International Corp. Windows, Windows 95 and Windows for Workgroups are registered trademarks and Windows NT is a trademark of Microsoft in the U.S. and other countries. Wyse is a registered trademark of Wyse Technology. Zentec is a trademark of Zentec Corporation. Other trademarks and brands are the property of their respective owners.

Copyright © 1991 - 1995 Intel Corporation, All Rights Reserved

| REVISION | HISTORY                          | DATE  |

|----------|----------------------------------|-------|

| -001     | Original Issue                   | 12/91 |

| -002     | Update for Release 2.0 of the OS | 08/92 |

| -003     | Update for Release 2.2 of the OS | 11/95 |

## **Quick Contents**

Chapter 1. Introduction

Chapter 2. Segmentation

**Chapter 3.** Program Linkage Directives

Chapter 4. Defining and Initializing Data

Chapter 5. Accessing Data

Chapter 6. Processor Instructions

Chapter 7. Floating-point Instructions

Chapter 8. Textmacros

Chapter 9. Codemacros

Appendix A. Processor Architecture Summary

Appendix B. Sample Program

Appendix C. Keywords and Reserved Words

Appendix D. ASCII Tables

Appendix E. Differences Between ASM386 and ASM286

Appendix F. Differences Between the Intel386™ and 376

**Processors**

Appendix G. Differences Between the Intel386 and Intel486™

**Processors**

Index

**Service Information**

## **Notational Conventions**

This manual uses the following conventions:

UPPERCASE In syntax descriptions, uppercase indicates keywords or

reserved words that must be spelled exactly as shown. They

can be entered in either uppercase or lowercase.

Within the text, uppercase indicates a mnemonic, operator,

or example code.

italic An item in italic is a metasymbol that may be replaced with

an item that fulfills the rules for that symbol.

In syntax descriptions, square brackets indicate an optional

part of a statement. If square brackets are required, the

syntax shows them in bold fact type, as [].

However, in certain register expressions, brackets are required within the actual statement. The descriptions of

such statements will indicate this requirement.

... In syntax descriptions, an ellipsis indicates that the preceding

argument or parameter may be repeated.

[....] In syntax descriptions, an ellipsis, preceded by a comma and

enclosed in brackets, indicates that the immediately preceding item may be repeated, but that each repetition

must be separated by a comma.

:: In examples, a vertical ellipsis indicates that some lines of

code have been omitted.

In syntax descriptions, any punctuation other than ellipses and brackets must be entered as shown. For example, the colon in the following syntax description must be included in a statement:

#### label:[instruction]

- User input, command syntax and computer output are printed like this, in regular monospaced text.

- In examples combining user input and computer output, user input is printed like this, in bold monospaced text.

Throughout this manual, the word "may" means "is permitted to".

#### Note

Notes indicate important information.

## $\Lambda$

#### **CAUTION**

Cautions indicate situations which may damage hardware or data.

## **Related Publications**

The following Intel manuals contain detailed information about processor architecture and the assembler for your development system:

- 80386 Programmer's Reference Manual, order number 230985, describes processor architecture from an application or system programmer's point of view.

- ASM386 Macro Assembler Operating Instructions, order number 451290 for DOS and 167675 for VAX/VMS, describes the assembler controls, assembler output, and assembler error messages.

- Intel386<sup>TM</sup> DX Microprocessor Hardware Reference Manual, order number 231732, describes the processor from a system engineer's or hardware designer's point of view.

The following Intel manuals contain detailed information about using floating-point coprocessors with the processor:

- 80386 Programmer's Reference Manual, order number 230985, Chapter 11, describes coprocessing and multiprocessing.

- 80387 Programmer's Reference Manual, order number 231917.

- *iAPX 286 Programmer's Reference Manual*, order number 210498, Numerics Supplement section, provides information about the Intel287<sup>TM</sup> coprocessor.

You may also need the processor systems utilities manual(s).

# Contents

| 1 | Introduction                                     |    |

|---|--------------------------------------------------|----|

|   | About This Manual                                | 23 |

|   | About This Chapter                               | 23 |

|   | Lexical Elements                                 | 24 |

|   | Character Set                                    | 24 |

|   | Tokens and Separators                            | 24 |

|   | Logical Spaces                                   | 25 |

|   | Delimiters                                       | 25 |

|   | Identifiers                                      | 26 |

|   | Continued Statements and Comments                | 26 |

|   | Assembler Statements                             | 29 |

|   | Assembler Directives                             | 29 |

|   | Assembler Instructions                           | 31 |

|   | Specifying Assembler Statements                  | 38 |

|   | Specifying Directive Statements                  | 38 |

|   | Specifying Instruction Statements                | 39 |

|   | Assembler Program Structure                      | 40 |

|   | NAME Directive                                   | 41 |

|   | STACKSEG Directive                               | 42 |

|   | SEGMENT Directive for Data Segments              | 42 |

|   | SEGMENT Directive for the Code Segment           | 43 |

|   | ASSUME Directive                                 | 44 |

|   | END Directive                                    | 45 |

|   | Initializing Segment Registers with Instructions | 45 |

|   | Initializing DS, ES, FS, and GS                  | 46 |

|   | Initializing SS                                  | 47 |

|   |                                                  |    |

| 2 | Segmentation                                     |    |

|   | Overview of Segmentation                         | 49 |

|   | Defining Code, Data, and Stack Segments          | 51 |

|   | SEGMENTENDS Directive                            | 51 |

|   | Specifying EO, ER, RO, or RW Access              | 52 |

|   | Specifying USE32 or USE16                        | 52 |

|   | Specifying PUBLIC or COMMON                          | 53       |

|---|------------------------------------------------------|----------|

|   | Multiple Definitions for a Segment                   | 54       |

|   | Lexically Nested or Embedded Segment Definitions     | 56       |

|   | STACKSEG Directive                                   | 57       |

|   | Combining Stack and Data Segments                    | 58       |

|   | Assuming Segment Access                              | 58       |

|   | ASSUME Directive                                     | 59       |

|   | Specifying Segment Selectors with ASSUME             | 60       |

|   | Specifying ASSUME NOTHING and ASSUME CS:NOTHING      | 63       |

|   |                                                      |          |

| 3 | Program Linkage Directives                           |          |

| _ | Modular Programming with NAME and END                | 67       |

|   | NAME Directive                                       | 68       |

|   | END Directive                                        | 69       |

|   | Defining Shared Data with PUBLIC, EXTRN, and COMM    | 71       |

|   | PUBLIC Directive                                     | 71       |

|   | EXTRN Directive                                      | 72       |

|   | Placement of EXTRN                                   | 73       |

|   | COMM Directive                                       | 74       |

|   | COMM Bilective                                       | , ¬      |

| 4 | Defining And Initializing Data                       |          |

| • | Overview of Assembler Labels and Variables           | 78       |

|   | Assembler Label and Variable Types                   | 78<br>78 |

|   | Assembler Data Values                                | 79       |

|   |                                                      | 80       |

|   | Data Types                                           | 81       |

|   | Numeric Data Value Ranges                            | 82       |

|   | Specifying Assembler Data Values                     | 82<br>83 |

|   | Initializing Variables                               |          |

|   | How the Assembler Evaluates Constant Expressions     | 83       |

|   | Variables                                            | 84       |

|   | Simple Data Allocations                              | 85       |

|   | Variable Attributes                                  | 86       |

|   | Defining and Initializing Variables of a Simple Type | 87       |

|   | DBIT Directive                                       | 87       |

|   | DB Directive                                         | 89       |

|   | DW Directive                                         | 90       |

|   | DD Directive                                         | 92       |

|   | DP Directive                                         | 94       |

|   | DQ Directive                                         | 96       |

|   | DT Directive                                         | 98       |

|   | Defining Compound Types and Their Variables          | 99       |

|   |                                                      |          |

|   | RECORD Directive                                  |

|---|---------------------------------------------------|

|   | Record Allocation Statement                       |

|   | STRUC Directive                                   |

|   | Structure Allocation Statement                    |

|   | DUP Clause                                        |

|   | Labels                                            |

|   | Label Attributes                                  |

|   | The Location Counter                              |

|   | ORG Directive                                     |

|   | EVEN Directive                                    |

|   | ALIGN Directive                                   |

|   | LABEL Directive                                   |

|   | Defining Implicit NEAR Labels                     |

|   | PROC Directive                                    |

|   | Using Symbolic Data                               |

|   | EQU Directive                                     |

|   | PURGE Directive                                   |

|   |                                                   |

| E | Accessing Date                                    |

| 5 | Accessing Data                                    |

|   | Overview of Assembler Expressions                 |

|   | Constant Expressions                              |

|   | Address Expressions                               |

|   | Variable and Label Names as Address Expressions   |

|   | Register Expressions                              |

|   | Combining Simple Address and Register Expressions |

|   | Structure Fields in Address Expressions           |

|   | Relocatable Expressions                           |

|   | Operators                                         |

|   | Operator Precedence                               |

|   | Isolation Operators                               |

|   | Multiplication and Division Operators             |

|   | Shift Operators                                   |

|   | Addition and Subtraction Operators                |

|   | Relational Operators                              |

|   | Logical Operators                                 |

|   | Attribute Value Operators                         |

|   | THIS Operator                                     |

|   | SEG Operator                                      |

|   | OFFSET Operator                                   |

|   | BITOFFSET Operator                                |

|   | LENGTH Operator                                   |

|   | TYPE Operator                                     |

|   | SIZE Operator                                      |  |

|---|----------------------------------------------------|--|

|   | STACKSTART Operator                                |  |

|   | Attribute Override Operators                       |  |

|   | Segment Override Operator                          |  |

|   | PTR Operator                                       |  |

|   | SHORT Operator                                     |  |

|   | Record Specific Operators                          |  |

|   | WIDTH Operator                                     |  |

|   | MASK Operator                                      |  |

|   | Using Field Names as Shift Counts                  |  |

|   | Instruction Operands                               |  |

|   | Register Operands                                  |  |

|   | Immediate Operands                                 |  |

|   | Memory Operands                                    |  |

|   | Memory Addressing Methods                          |  |

|   | Direct Memory Addressing.                          |  |

|   | Indirect Memory Addressing                         |  |

|   | Register Indirect Addressing                       |  |

|   | Based Addressing                                   |  |

|   | Based Indexed Addressing                           |  |

|   | Indexed Addressing                                 |  |

|   | Scaling                                            |  |

|   | Default Segment Registers and Anonymous References |  |

|   | Bit Addressing                                     |  |

|   |                                                    |  |

| 3 | Processor Instructions                             |  |

|   | Overview of the Processor Instruction Set          |  |

|   | Data Transfer Instructions                         |  |

|   | Instructions That Assign Data Values               |  |

|   | Instructions That Adjust Data                      |  |

|   | Instructions That Make Stack Transfers             |  |

|   | Instructions That Yield Definitive Flag Values     |  |

|   | Conditional Instructions That Test Flag Values     |  |

|   | Control Instructions                               |  |

|   | System Instructions                                |  |

|   | Instruction Statements                             |  |

|   | Instruction Statement Syntax                       |  |

|   | Instruction Attributes                             |  |

|   | Address Size Attribute                             |  |

|   | Operand Size Attribute                             |  |

|   | Stack Size Attribute                               |  |

|   |                                                    |  |

| Instruction Encoding Format                         |  |

|-----------------------------------------------------|--|

| Instruction Prefix Codes                            |  |

| ModRM and SIB Bytes                                 |  |

| Processor Instruction Set Reference                 |  |

| How to Read the Instruction Set Reference Pages     |  |

| Opcode Column                                       |  |

| Instruction Column                                  |  |

| Clocks Column                                       |  |

| Description Column                                  |  |

| Operation Section                                   |  |

| Discussion Section                                  |  |

| Flags Affected Section                              |  |

| Exceptions by Mode Section                          |  |

| How to Look Up an Instruction                       |  |

| Processor Instructions                              |  |

| AAA ASCII Adjust after Addition                     |  |

| AAD ASCII Adjust AX before Division                 |  |

| AAM ASCII Adjust AX after Multiply                  |  |

| AAS ASCII Adjust AL after Subtraction               |  |

| ADC Add with Carry                                  |  |

| ADD (Integer) Add                                   |  |

| AND Logical AND                                     |  |

| ARPL Adjust RPL Field of Selector                   |  |

| BOUND Check Array Index Against Bounds              |  |

| BSF Bit Scan Forward                                |  |

| BSR Bit Scan Reverse                                |  |

| BSWAP Byte Swap (not available on Intel386 or       |  |

| 376 processors)                                     |  |

| BT Bit Test                                         |  |

| BTC Bit Test and Complement                         |  |

| BTR Bit Test and Reset                              |  |

| BTS Bit Test and Set                                |  |

| CALL Call Procedure                                 |  |

| CBW/CWDE Convert Byte to Word/Convert Word to Dword |  |

| CLC Clear Carry Flag                                |  |

| CLD Clear Direction Flag                            |  |

| CLI Clear Interrupt Flag                            |  |

| CLTS Clear Task Switched Flag in CR0                |  |

| CMC Complement Carry Flag                           |  |

| CMP Compare Two Operands                            |  |

| CMPS/CMPSB/CMPSW/CMPSD Compare String Operands      |  |

| CMPXCHG Compare Exchange (not available on Intel386 |  |

| or 376 processors)                                  |  |

## 6 Processor Instructions (continued)

| CWD/CDQ Convert Word to Dword/Convert Dword to Qword         | 265 |

|--------------------------------------------------------------|-----|

| DAA Decimal Adjust AL after Addition                         | 267 |

| DAS Decimal Adjust AL after Subtraction                      | 268 |

| DEC Decrement by 1                                           | 269 |

| DIV Unsigned Divide                                          | 270 |

| ENTER Make Stack Frame for Procedure Parameters              | 272 |

| HLT Halt                                                     | 274 |

| IDIV Signed Divide                                           | 275 |

| IMUL Signed Multiply                                         | 277 |

| IN Input from Port                                           | 280 |

| INC Increment by 1                                           | 282 |

| INS/INSB/INSW/INSD Input from Port to String                 | 283 |

| INT/INTO Transfer Control to Interrupt Procedure             | 286 |

| INVD Invalidate Data Cache (not available on Intel386 or 376 |     |

| processors)                                                  | 292 |

| INVLPG Invalidate Paging Cache Entry (not available on       |     |

| Intel386 or 376 processors)                                  | 293 |

| IRET/IRETD Interrupt Return                                  | 294 |

| Jcc Jump if Condition is Met                                 | 299 |

| JMP Jump                                                     | 304 |

| LAHF Load Flags into AH Register                             | 310 |

| LAR Load Access Rights                                       | 311 |

| LDS/LES/LFS/LGS/LSS Load Full Pointer                        | 314 |

| LEA Load Effective Address                                   | 317 |

| LEAVE High Level Procedure Exit                              | 319 |

| LGDT/LIDT Load Global/Interrupt Descriptor Table Register    | 320 |

| LGDTW/LGDTD/LIDTW/LIDTD Load Global/Interrupt                |     |

| Descriptor Table Register with WORD/DWORD Operand            | 322 |

| LLDT Load Local Descriptor Table Register                    | 324 |

| LMSW Load Machine Status Word                                | 326 |

| LOCK Assert Bus LOCK# Signal Prefix                          | 327 |

| LODS/LODSB/LODSW/LODSD Load String Operand                   | 329 |

| LOOP/LOOPcond Loop Control with (E)CX Counter                | 331 |

| LSL Load Segment Limit                                       | 333 |

| LTR Load Task Register                                       | 336 |

| MOV Move Data                                                | 338 |

| MOV Move to/from Special Registers                           | 341 |

| MOVS/MOVSB/MOVSW/MOVSD Move String to String                 | 343 |

| MOVSX Move with Sign-Extend                                  | 346 |

| MOVZX Move with Zero-Extend                                  | 347 |

| MUL Unsigned Multiplication of AL, AX or EAX                 | 348 |

| NEG Two's Complement Negation                                | 350 |

| NOP No Operation                                              | 51            |

|---------------------------------------------------------------|---------------|

| NOT One's Complement Negation                                 | 52            |

| OR Logical Inclusive OR                                       | 53            |

| OUT Output to Port                                            | 55            |

| OUTS/OUTSB/OUTSW/OUTSD Output String to Port                  | 57            |

| POP Pop Stack Top                                             | 6(            |

| POPA/POPAD Pop All General Registers                          | 63            |

|                                                               | 65            |

| PUSH Push Operand onto the Stack                              | 57            |

| PUSHA/PUSHAD Push all General Registers                       | 69            |

| PUSHF/PUSHFD Push Flags Register onto the Stack               | 71            |

| RCL/RCR/ROL/ROR Rotate                                        | 72            |

| RET Return from Procedure                                     | 81            |

| SAHF Store AH into Flags                                      | 36            |

| SAL/SAR/SHL/SHR Shift                                         | 87            |

| SBB Integer Subtraction with Borrow                           | 91            |

| SCAS/SCASB/SCASW/SCASD Compare String Data                    | 93            |

| SETcc Byte Set on Condition                                   | 95            |

| SGDT/SIDT Store Global/Interrupt Descriptor Table Register 39 | 97            |

| SGDTW/SGDTD/SIDTW/SIDTD Store Global/Interrupt                |               |

|                                                               | 99            |

| SHLD Double Precision Shift Left                              | $\mathcal{C}$ |

| SHRD Double Precision Shift Right                             | )2            |

| 3                                                             | 04            |

| SMSW Store Machine Status Word                                | )5            |

| STC Set Carry Flag                                            | 06            |

| STD Set Direction Flag                                        | 07            |

| STI Set Interrupt Flag                                        | 96            |

| STOS/STOSB/STOSW/STOSD Store String Data                      | 09            |

| STR Store Task Register                                       | 11            |

| SUB Integer Subtraction                                       | 12            |

| TEST Logical Compare                                          |               |

| VERR/VERW Verify a Segment for Reading or Writing 4           | 16            |

| WAIT Wait until BUSY# Pin is Inactive (HIGH)                  | 18            |

| WBINVD Write Back And Invalidate Data Cache                   |               |

| (not available on Intel386 or 376 processors)                 | 19            |

| XADD Exchange Add (not available on Intel386 or               |               |

| 376 processors)                                               | 20            |

| XCHG Exchange Register/Memory with Register                   |               |

| XLAT/XLATB Table Look-up Translation                          |               |

| YOR Logical Evelusive OR                                      | 16            |

| 7 | Floating-Point Instructions                                |     |

|---|------------------------------------------------------------|-----|

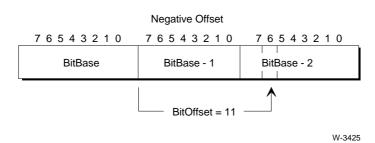

|   | Floating-point Coprocessor Architecture                    | 429 |

|   | Floating-point Stack                                       | 430 |

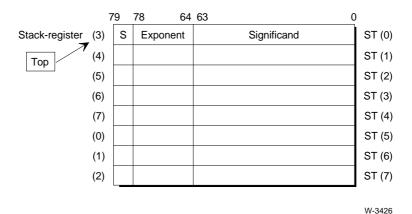

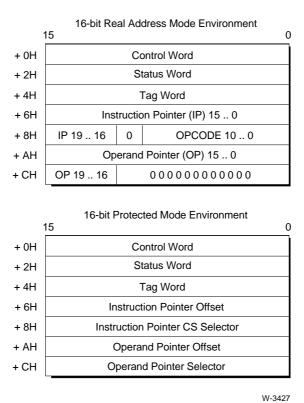

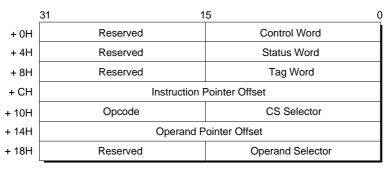

|   | Environment                                                | 431 |

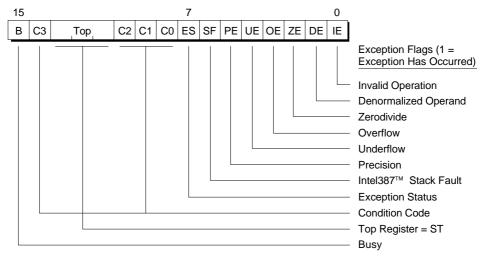

|   | Status Word                                                | 433 |

|   | Control Word                                               | 435 |

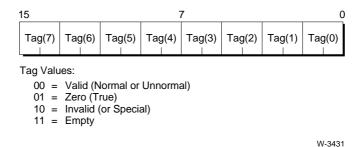

|   | Tag Word                                                   | 438 |

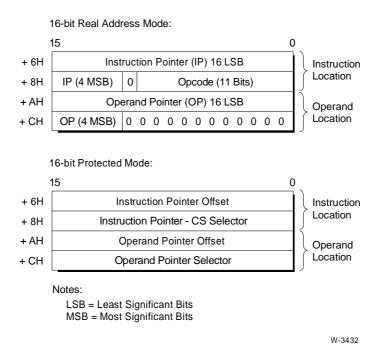

|   | Operation Locator Formats                                  | 439 |

|   | Floating-point Coprocessor Data Formats                    | 440 |

|   | Coprocessor Operation                                      | 443 |

|   | Numeric Processing                                         | 444 |

|   | Overview of the Floating-point Coprocessor Instruction Set | 446 |

|   | Data Transfer Instructions                                 | 446 |

|   | Constant Instructions                                      | 447 |

|   | Algebraic Instructions                                     | 448 |

|   | Comparison Instructions                                    | 451 |

|   | Transcendental Instructions                                | 452 |

|   | Coprocessor Control Instructions                           | 453 |

|   | Floating-point Coprocessor Instruction Set Reference       | 454 |

|   | How to Read the Instruction Set Reference Pages            | 454 |

|   | Opcode Column                                              | 454 |

|   | Instruction Column                                         | 455 |

|   | Clocks Columns                                             | 455 |

|   | Description Column.                                        | 455 |

|   | Discussion Section                                         | 456 |

|   | Exceptions Section                                         | 456 |

|   | How to Look Up an Instruction                              | 456 |

|   | F2XM1 Compute $Y = 2^X - 1$                                | 457 |

|   | FABS Absolute Value                                        | 458 |

|   | FADD/FADDP Real Addition                                   | 459 |

|   | FBLD BCD Load to Real                                      | 460 |

|   | FBSTP BCD Store and Pop                                    | 461 |

|   | FCHS Change Sign of Real Number                            | 462 |

|   | FCLEX/FNCLEX Clear Floating-point Coprocessor Exceptions   | 463 |

|   | FCOM/FCOMP/FCOMPP Compare Real Numbers                     | 464 |

|   | FCOS Compute $Y = Cos(X)$                                  | 466 |

|   | FDECSTP Decrement Floating-point Stack Pointer             | 467 |

|   | FDIV/FDIVP/FDIVR/FDIVRP Real Divide/Real                   | 407 |

|   |                                                            | 468 |

|   | Reverse Divide                                             |     |

|   | FFREE Free Floating-point Stack Entry                      | 469 |

|   | FIADD Integer Add to Real                                  | 470 |

|   | FICOM/FICOMP Integer Compare with Real                     | 471 |

| FIDIV/FIDIVR Integer Divide into Real                     | 4   |

|-----------------------------------------------------------|-----|

| FILD Integer Load into Real                               | 4   |

| FIMUL Integer Multiply with Real                          | 4   |

| FINCSTP Increment Floating-point Stack Pointer            | 4   |

| FINIT/FNINIT Initialize Floating-point Coprocessor        | 4′  |

| FIST/FISTP Integer Store from Real                        | 47  |

| FISUB/FISUBR Integer Subtract from Real                   | 48  |

| FLD Load Real                                             | 48  |

| FLDCW Load Floating-point Coprocessor Control Word        | 48  |

| FLDENV Load Floating-point Coprocessor Environment        | 48  |

| FLDcon Load Real Constant                                 | 48  |

| FMUL/FMULP Multiply Real                                  | 48  |

| FNOP No Operation                                         | 48  |

| FPATAN Compute R = Partial Arctangent                     | 48  |

| FPREM/FPREM1 Partial Remainder                            | 48  |

| FPTAN Compute Y = Partial Tan(X)                          | 49  |

| FRNDINT Round to Integer                                  | 49  |

| FRSTOR Restore Floating-point Coprocessor Machine State   | 40  |

| FSAVE/FNSAVE Save Floating-point Coprocessor              | •   |

| Machine State                                             | 49  |

| FSCALE Scale Exponent of Real                             | 49  |

| FSETPM Set Protected Mode                                 | 5(  |

| FSIN Compute $Y = Sin(X)$                                 | 50  |

| FSINCOS Compute $Y = Sin(X)$ and $Y = Cos(X)$             | 50  |

| FSQRT Square Root                                         | 50  |

| FST/FSTP Store Real/Store Real and Pop                    | 50  |

| FSTCW/FNSTCW Store Floating-point Coprocessor             | 5   |

| Control Word                                              | 50  |

| FSTENV/FNSTENV Store Floating-point Coprocessor           | 50  |

| Environment                                               | 50  |

| FSTSW/FNSTSW Store Floating-point Coprocessor Status Word | 50  |

| FSUB/FSUBP/FSUBR/FSUBRP Subtract Real                     | 50  |

|                                                           | 5(  |

| FTST Test Real (Compare to Zero)                          | )(  |

| FUCOM/FUCOMP/FUCOMPP Unordered Comparison of              | ۔ ۔ |

| Real Numbers                                              | 5   |

| FWAIT Wait for Floating-point Operation Complete          | 51  |

| FXAM Examine Floating-point Stack Top                     | 5   |

| FXCH Exchange Real Numbers in Stack                       | 5   |

| FXTRACT Extract Exponent and Significand of Real          | 51  |

| FYL2X Compute Y * log <sub>2</sub> X                      | 5   |

| FYL2XP1 Compute $Y * log_2(X + 1)$                        | 5   |

| Textmacros                                          |

|-----------------------------------------------------|

| Overview                                            |

| Macro Processing                                    |

| Macro Calls and Call Patterns                       |

| Macro Processor Scanning Modes and Macro Expansions |

| Predefined Macros                                   |

| Macro Arguments                                     |

| Balanced Text                                       |

| Delimiters in Call Patterns                         |

| Identifiers                                         |

| Expressions                                         |

| Argument Evaluations                                |

| Predefined Macro Reference                          |

| DEFINE Macro                                        |

| Bracket Macro                                       |

| Escape Macro                                        |

| Comment Macro                                       |

| METACHAR Macro                                      |

| EVAL Macro                                          |

| SET Macro                                           |

| IF Macro                                            |

| WHILE Macro                                         |

| REPEAT Macro                                        |

| EXIT Macro                                          |

| String Comparison Macros                            |

| LEN Macro                                           |

| SUBSTR Macro                                        |

| MATCH Macro                                         |

| Console I/O Macros                                  |

| Scanning Modes, Delimiters, and Macro Expansions    |

| Normal and Literal Scanning Modes                   |

| Macro Delimiters                                    |

| Literal Delimiters                                  |

| Implied Blank Delimiters                            |

| Identifier Delimiters                               |

Algorithm for Evaluating Macro Calls.....

556

| Codemacros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Codemacro Definitions and Calls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Processor Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Codemacro Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CODEMACRO Directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Formal Parameters and Specifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Formal Parameter Modifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Formal Parameter Range Specifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PREFIX67 Directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PREFIX66 Directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SEGFIX Directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NOSEGFIX Directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WARNING Directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MODRM Directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Data Initialization Directives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Record Initialization Directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Using the Dot Operator to Shift Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PROCLEN Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Relative Displacement Directives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Matching Codemacro Calls to Their Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Matching Codemacro Calls to Their Definitions  Processor Architecture Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Matching Codemacro Calls to Their Definitions  Processor Architecture Summary Basic Processor Formats.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Matching Codemacro Calls to Their Definitions  Processor Architecture Summary  Basic Processor Formats  Data Type Formats                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Processor Architecture Summary Basic Processor Formats. Data Type Formats. Processor Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Matching Codemacro Calls to Their Definitions  Processor Architecture Summary  Basic Processor Formats.  Data Type Formats.  Processor Registers.  General, Segment, Status and Instruction Registers.                                                                                                                                                                                                                                                                                                                                    |

| Processor Architecture Summary Basic Processor Formats. Data Type Formats. Processor Registers. General, Segment, Status and Instruction Registers System Registers.                                                                                                                                                                                                                                                                                                                                                                      |

| Processor Architecture Summary Basic Processor Formats. Data Type Formats. Processor Registers. General, Segment, Status and Instruction Registers System Registers. Processor Memory Organization                                                                                                                                                                                                                                                                                                                                        |

| Processor Architecture Summary Basic Processor Formats Data Type Formats Processor Registers General, Segment, Status and Instruction Registers System Registers Processor Memory Organization Segment Selection and Effective Address Computation.                                                                                                                                                                                                                                                                                       |

| Processor Architecture Summary Basic Processor Formats Data Type Formats Processor Registers General, Segment, Status and Instruction Registers System Registers Processor Memory Organization Segment Selection and Effective Address Computation. Segmented Memory Management                                                                                                                                                                                                                                                           |

| Processor Architecture Summary  Basic Processor Formats.  Data Type Formats.  Processor Registers.  General, Segment, Status and Instruction Registers  System Registers.  Processor Memory Organization  Segment Selection and Effective Address Computation.  Segmented Memory Management  Segment Descriptors.                                                                                                                                                                                                                         |

| Processor Architecture Summary  Basic Processor Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Processor Architecture Summary  Basic Processor Formats.  Data Type Formats.  Processor Registers.  General, Segment, Status and Instruction Registers  System Registers.  Processor Memory Organization  Segment Selection and Effective Address Computation.  Segment Descriptors.  Descriptor Address Translation Fields  Descriptor Access Rights (AR)                                                                                                                                                                                |

| Processor Architecture Summary  Basic Processor Formats.  Data Type Formats.  Processor Registers.  General, Segment, Status and Instruction Registers  System Registers.  Processor Memory Organization  Segment Selection and Effective Address Computation.  Segmented Memory Management  Segment Descriptors.  Descriptor Address Translation Fields  Descriptor Tables and Selector Format.                                                                                                                                          |

| Processor Architecture Summary  Basic Processor Formats  Data Type Formats  Processor Registers  General, Segment, Status and Instruction Registers  System Registers  Processor Memory Organization  Segment Selection and Effective Address Computation.  Segmented Memory Management  Segment Descriptors.  Descriptor Address Translation Fields  Descriptor Tables and Selector Format  Processor Protection, Gate Descriptors, and Task Switches                                                                                    |

| Processor Architecture Summary  Basic Processor Formats  Data Type Formats  Processor Registers  General, Segment, Status and Instruction Registers  System Registers  Processor Memory Organization  Segment Selection and Effective Address Computation.  Segmented Memory Management  Segment Descriptors.  Descriptor Address Translation Fields  Descriptor Tables and Selector Format  Processor Protection, Gate Descriptors, and Task Switches  Protection and Privilege Levels                                                   |

| Processor Architecture Summary  Basic Processor Formats  Data Type Formats  Processor Registers  General, Segment, Status and Instruction Registers  System Registers  Processor Memory Organization  Segment Selection and Effective Address Computation  Segmented Memory Management  Segment Descriptors  Descriptor Address Translation Fields  Descriptor Tables and Selector Format  Processor Protection, Gate Descriptors, and Task Switches  Protected Control Transfers Use Gate Descriptors                                    |

| Processor Architecture Summary  Basic Processor Formats.  Data Type Formats.  Processor Registers.  General, Segment, Status and Instruction Registers  System Registers.  Processor Memory Organization  Segment Selection and Effective Address Computation.  Segmented Memory Management  Segment Descriptors.  Descriptor Address Translation Fields  Descriptor Tables and Selector Format  Processor Protection, Gate Descriptors, and Task Switches  Protected Control Transfers Use Gate Descriptors  Call Gate Descriptor Format |

| Processor Architecture Summary  Basic Processor Formats.  Data Type Formats.  Processor Registers.  General, Segment, Status and Instruction Registers  System Registers.  Processor Memory Organization  Segment Selection and Effective Address Computation.  Segmented Memory Management.  Segment Descriptors.  Descriptor Address Translation Fields  Descriptor Tables and Selector Format.  Processor Protection, Gate Descriptors, and Task Switches  Protected Control Transfers Use Gate Descriptors.                           |

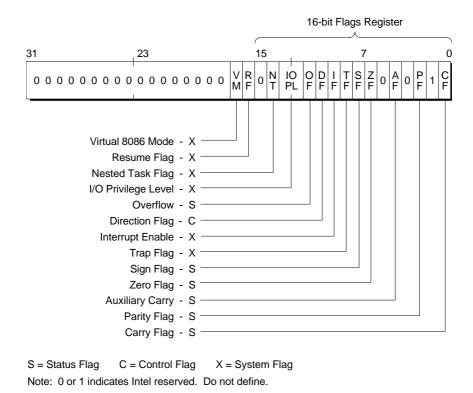

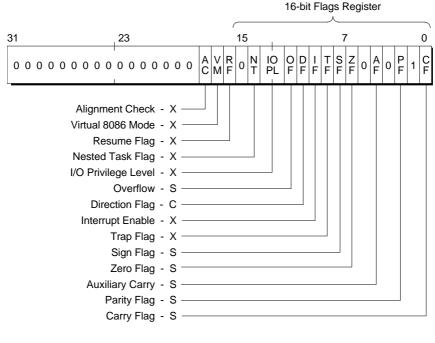

| Processor Flags                                         | ( |

|---------------------------------------------------------|---|

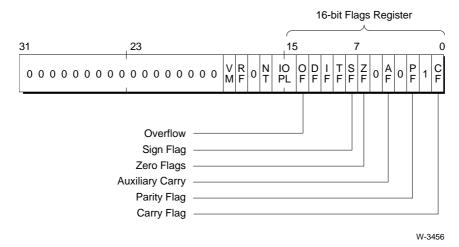

| Status Flags                                            | ( |

| Carry Flag                                              | ( |

| Parity Flag                                             | ( |

| Auxiliary Carry Flag                                    |   |

| Zero Flag                                               | ( |

| Sign Flag                                               | ( |

| Overflow Flag                                           |   |

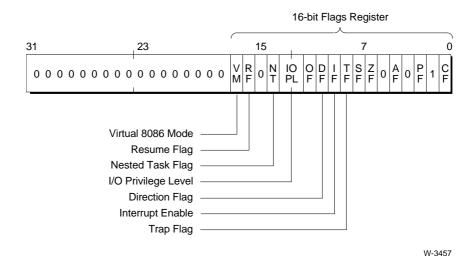

| Control and System Control Flags                        |   |

| Processor Exceptions and Interrupts                     |   |

| Identifying Interrupts                                  |   |

| Simultaneous Exceptions and Interrupts                  |   |

| Interrupt Descriptor Table                              |   |

| Error Codes for Exceptions                              |   |

| Processor Exception Conditions                          |   |

| Interrupt 0 Divide Error                                |   |

| Interrupt 1 Debug Exceptions                            |   |

| Interrupt 2 NMI                                         |   |

| Interrupt 3 Breakpoint                                  |   |

| Interrupt 4 Overflow                                    |   |

| Interrupt 5 Bounds Check                                |   |

| #UD 6 Undefined Opcode (No Error Code)                  |   |

| #NM 7 No Math Unit Available (No Error Code)            |   |

| #DF 8 Double Fault (Zero Error Code)                    |   |

| Interrupt 9 Coprocessor Segment Overrun                 |   |

| #TS 10 Invalid Task State Segment (Selector Error Code) |   |

| #NP 11 Not Present (Selector Error Code)                |   |

| #SS 12 Stack Fault (Selector or Zero Error Code)        |   |

| #GP 13 General Protection (Selector or Zero Error Code) |   |

| #PF 14 Page Fault (Type of Fault)                       |   |

| #MF 16 Math Fault (No Error Code)                       |   |

| Campula Dua mana                                        |   |

| Sample Program                                          |   |

| Sample Source Code                                      |   |

| Sample Listing                                          |   |

|                                                         |   |

| Keywords And Reserved Words                             |   |

|                                                         |   |

| D    | ASCII Tables                                                 | 655  |

|------|--------------------------------------------------------------|------|

|      |                                                              |      |

| Е    | Differences Between ASM386 and ASM286                        | 659  |

|      | New Processor Registers                                      | 659  |

|      | New Instructions                                             | 659  |

|      | Processor Paging Mechanism                                   | 660  |

|      | Addressing Differences                                       | 660  |

|      | Data Types                                                   | 661  |

|      | Bit Manipulation                                             | 661  |

|      | Assembler Directives                                         | 661  |

|      | Assembler Operators                                          | 661  |

|      | Assembler Arithmetic                                         | 662  |

|      | Prefix66 and Prefix67 Codemacro Directives                   | 662  |

| F    | Differences Between the Intel386™ and 376 Processors         | 663  |

| G    | Differences Between the Intel386 and Intel486™<br>Processors | 667  |

| Inde | ex                                                           | 669  |

| Ser  | vice Information Inside Back                                 | Cove |

| Table | es                                                       |

|-------|----------------------------------------------------------|

| 1-1.  | Assembler Directives                                     |

| 1-2.  | Processor Instructions                                   |

| 1-3.  | Floating-point Instructions                              |

| 4-1.  | Assembler Variable Types and Numerical Value Ranges      |

| 4-2.  | Assembler Data Value Specification Rules                 |

| 5-1.  | Assembler Operators                                      |

| 5-2.  | Assembler Operator Precedence                            |

| 5-3.  | TYPE Operator Results                                    |

| 5-4.  | PTR Result Attributes                                    |

| 6-1.  | External I/O Instructions                                |

| 6-2.  | Internal Load and Store Instructions                     |

| 6-3.  | Instructions That Make Uncalculated Value Assignments    |

| 6-4.  | Instructions That Make Calculated Value Assignments      |

| 6-5.  | Data Conversion Instructions                             |

| 6-6.  | Shift and Rotate Instructions                            |

| 6-7.  | Stack Transfer Instructions                              |

| 6-8.  | Processor Instructions That Yield Definitive Flag Values |

| 6-9.  | Conditional Instructions That Test Flag Values           |

| 6-10. | Control Transfer Instructions                            |

| 6-11. | Processor Control Instructions                           |

| 6-12. | Generation of Address and Operand Size Prefixes          |

| 6-13. | 16-Bit Addressing Forms with ModRM Byte in Hexadecimal   |

| 6-14. | 32-Bit Addressing Forms with ModRM Byte in Hexadecimal   |

| 6-15. | 32-Bit Addressing Forms with SIB Byte in Hexadecimal     |

| 6-16. | Processor Exceptions and Interrupts                      |

| 6-17. | Operands and Implicit Destinations for DIV               |

| 6-18. | Operands and Implicit Destinations for IDIV              |

| 6-19. | When IMUL Clears CF and OF                               |

| 6-20. | JMP Label Types, Operand Sizes and Instructions          |

| 6-21. | System Descriptor Types for LAR                          |

| 6-22. | System Descriptor Types for LSL                          |

| 7-1.  | Summary of Real Format Parameters                        |

| 7-2.  | Rounding Methods                                         |

| 7-3.  | Data Transfer Instructions                               |

| 7-4.  | Constant Instructions                                    |

| 7-5.  | Algebraic Instructions                                   |

| 7-6.  | Basic Arithmetic Instruction and Operand Forms           |

| 7-7.  | Comparison Instructions                                  |

| 7-8.  | Transcendental Instructions                              |

| 7-9.  | Processor Control Instructions                           |

| 7-10  | Condition Code after FCOM(P/PP)                          |

| 7-11.                     | Condition Code after FICOM(P)                               | 47 |

|---------------------------|-------------------------------------------------------------|----|

| 7-12.                     | Floating-point Coprocessor State Following FINIT/FNINIT     | 47 |

| 7-13.                     | FPATAN Final Result Octant                                  | 48 |

| 7-14.                     | Condition Code after FPREM/FPREM1                           | 49 |

| 7-15.                     | Condition Code after FTST                                   | 50 |

| 7-16.                     | Condition Code after FUCOM(P/PP)                            | 51 |

| 7-17.                     | Condition Code after FXAM                                   | 5  |

| 8-1.                      | Predefined Macros                                           | 52 |

| 8-2.                      | Predefined Macro Call Patterns                              | 52 |

| 9-1.                      | Codemacro Syntax Summary                                    | 56 |

| A-1.                      | Default Segment Register Selection Rules                    | 59 |

| A-2.                      | Processor Exceptions and Interrupts                         | 62 |

| C-1.                      | Assembler Keywords                                          | 65 |

| C-2.                      | Assembler Reserved Words                                    | 65 |

| D-1.                      | ASCII Collating Sequence                                    | 65 |

| D-2.                      | ASCII Non-Printable Characters                              | 65 |

|                           |                                                             |    |

| Figu                      |                                                             |    |

| 1 igu<br>1-1.             |                                                             | 2  |

| 1-1.<br>1-2.              | Template for an Assembler Program                           | 2  |

| 4-1.                      | An ASM386 Example Program                                   | 10 |

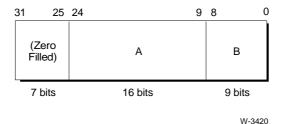

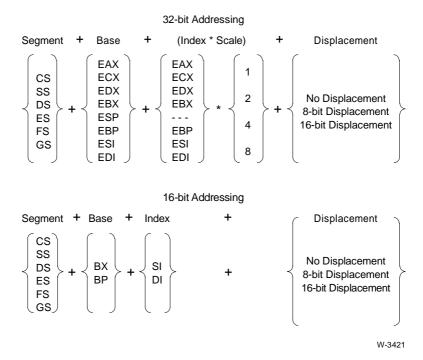

| 5-1.                      | Effective Address Calculation                               | 16 |

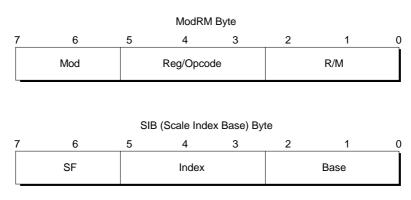

| 6-1.                      | Instruction Encoding Format                                 | 18 |

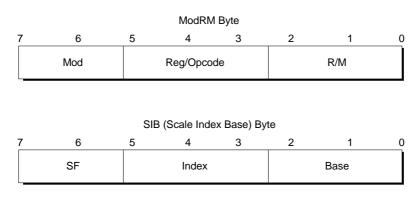

| 6-2.                      | ModRM and SIB Byte Formats                                  | 18 |

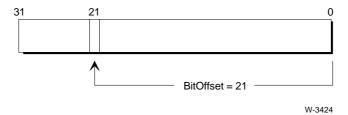

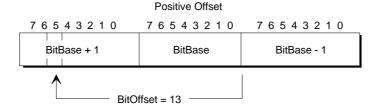

| 6-3.                      | BitOffset for BIT[EAX,21]                                   | 20 |

| 6-4.                      | Memory Bit Indexing                                         | 20 |

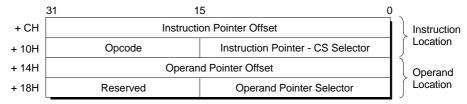

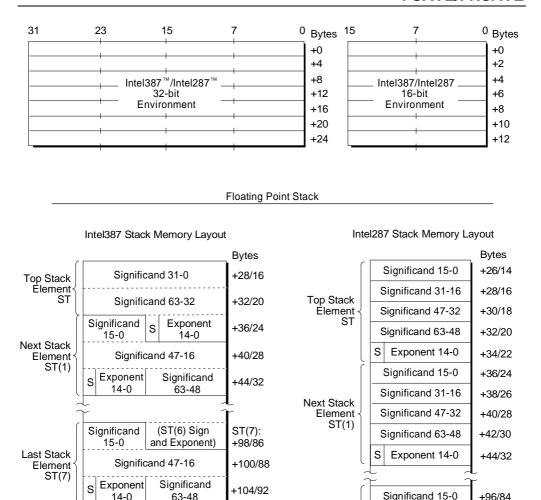

| 7-1.                      | Floating-point Coprocessor Stack Fields                     | 43 |

| 7-1.<br>7-2.              | 16-bit Environments                                         | 43 |

| 7-2.<br>7-3.              | 32-bit Environments.                                        | 43 |

| 7-3.<br>7-4.              | Status Word Format                                          | 43 |

| 7- <del>4</del> .<br>7-5. | Control Word Format                                         | 43 |

| 7-5.<br>7-6.              | Tag Word Format                                             | 43 |

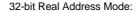

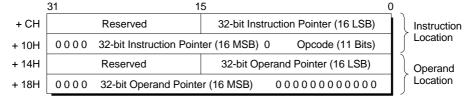

| 7-0.<br>7-7.              | 16-bit Opcode, IP, and Op Environment Formats               | 43 |

| 7-7.<br>7-8.              | 32-bit Opcode, IP, and OP Environment Formats               | 44 |

| 7-0.<br>7-9.              | Data Formats                                                | 44 |

| 7-10.                     | Floating-point Coprocessor Machine State Layout after FSAVE | 49 |

| 9-1.                      | Instruction Encoding Format                                 | 56 |

| 9-2.                      | ModRM and SIB Byte Formats                                  | 56 |

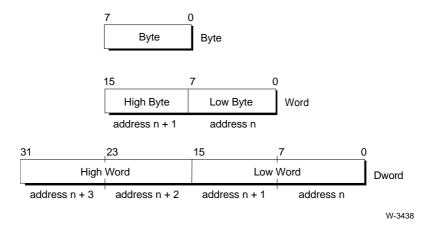

| A-1.                      | Fundamental Data Types                                      | 58 |

| A-2.                      | Processor Data Types and Storage Formats                    | 58 |

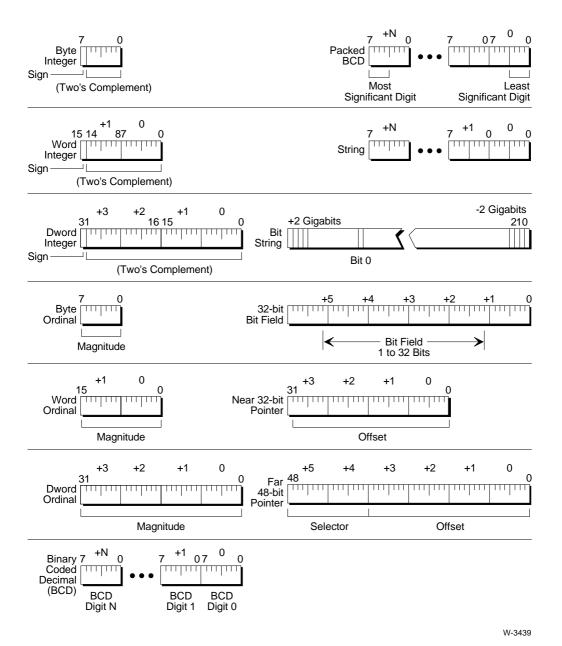

| A-3.                      | General, Segment, Status, and Instruction Registers         | 59 |

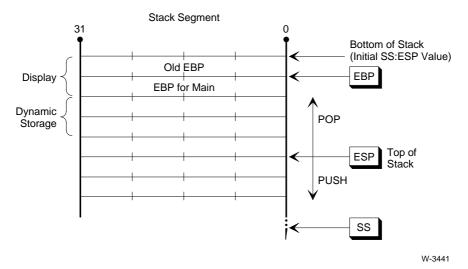

| A-4.                      | Processor Stack with Stack Frame                            | 59 |

|                           |                                                             | -  |

## **Figures (continued)**

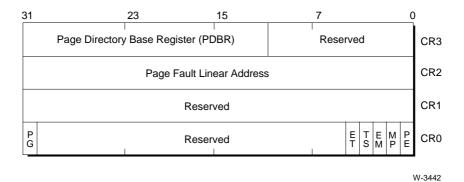

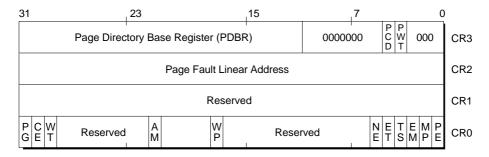

| A-5.  | System Control Registers                             | 594 |

|-------|------------------------------------------------------|-----|

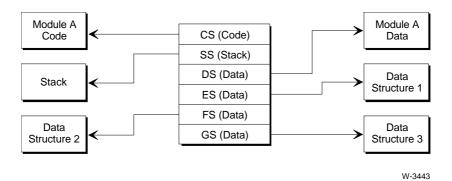

| A-6.  | Memory Segmentation Model for ASM386 Programs        | 596 |

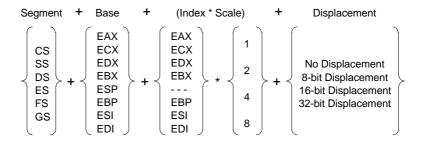

| A-7.  | Effective Address Calculation                        | 598 |

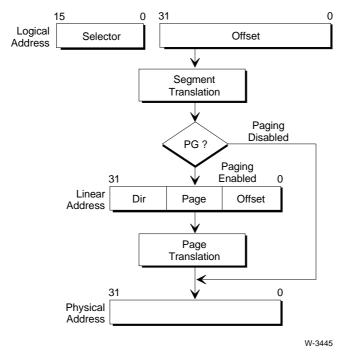

| A-8.  | Processor Address Translation Overview               | 599 |

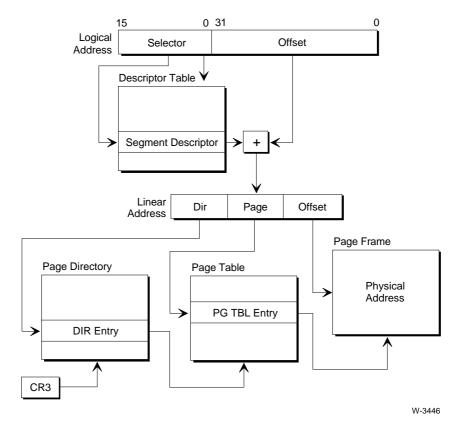

| A-9.  | Segment Address Translation in a Paged System        | 600 |

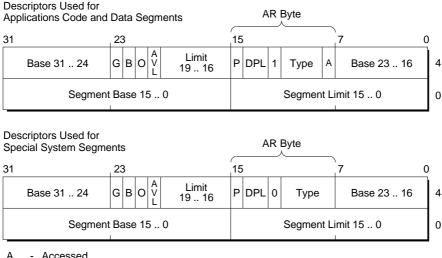

| A-10. | General Segment Descriptor Formats                   | 601 |

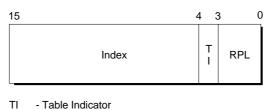

| A-11. | Selector Format                                      | 603 |

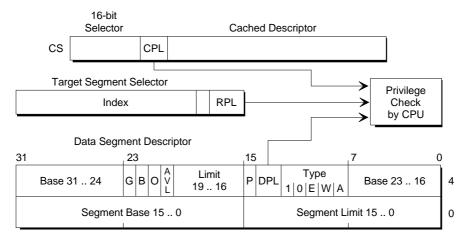

| A-12. | Processor Privilege Check for Data Access            | 605 |

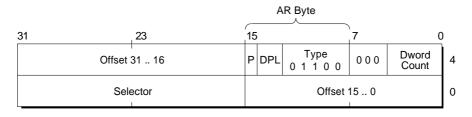

| A-13. | Call Gate Descriptor Format                          | 607 |

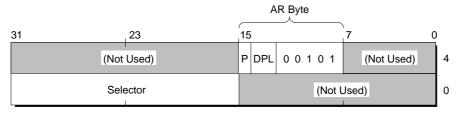

| A-14. | Task Gate Descriptor Format                          | 607 |

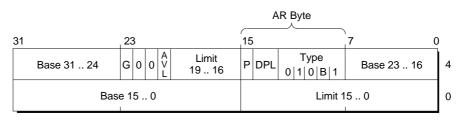

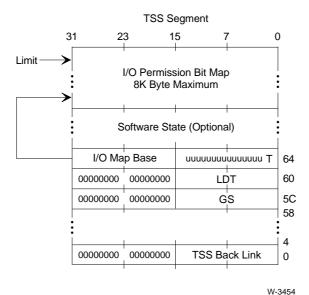

| A-15. | TSS Descriptor Format for 32-bit TSS                 | 608 |

| A-16. | General Segment Descriptor Formats                   | 609 |

| A-17. | I/O Address Bit Map                                  | 611 |

| A-18. | Processor EFLAGS Register                            | 612 |

| A-19. | Status Flags Format                                  | 613 |

| A-20. | Control Flags and IOPL Format                        | 616 |

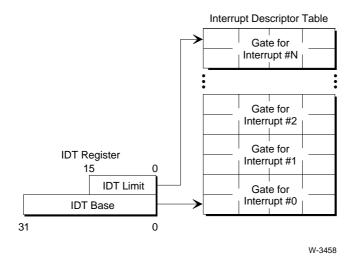

| A-21. | Interrupt Descriptor Table and Register              | 62  |

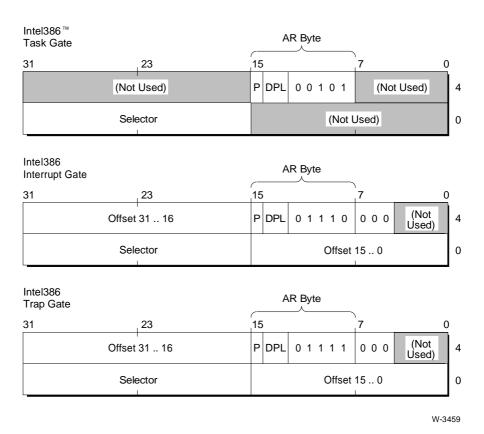

| A-22. | IDT Gate Descriptors                                 | 622 |

| G-1.  | Intel486 Processor Control Registers                 | 669 |

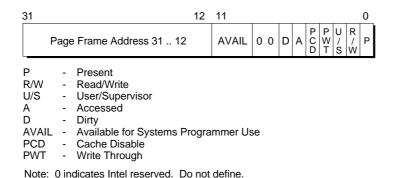

| G-2.  | Intel486 Processor Page Table/Directory Entry Format | 669 |

| G-3.  | Intel486 Processor EFLAGS Register                   | 670 |

## **About This Manual**

ASM386 supports the Pentium® and Intel486<sup>™</sup> microprocessors and the entire Intel386<sup>™</sup> family, including the Intel386, Intel386 SX, and 376 microprocessors, as well as the Intel287<sup>™</sup>, Intel387<sup>™</sup> and Intel387 SX floating-point coprocessors. Throughout this manual, the word "processor" refers to any of the above microprocessors and the words "floating-point coprocessor" refer to any of the above coprocessors, as well as the Pentium and Intel486 processors' built-in floating-point functions.

This manual is a reference for the ASM386 assembly language. It assumes that you are familiar with assembly language programming and 8086/286/Intel386 processor architecture. Read Appendix A if you are already familiar with the 8086/286 processor architecture(s). If you aren't, see the 80386 Programmer's Reference Manual.

## **About This Chapter**

This chapter introduces the assembly language. It has three major sections:

#### Lexical Elements

This section describes the assembler character set, tokens, separators, identifiers, comments, and the difference between source file lines and logical statement lines.

#### Statements

This section introduces the assembler directives, processor instruction set, and floating-point instruction set.

#### Program Structure

This section provides a template for assembler programs together with a simple example program (see Appendix B for another example program). It summarizes the essential parts of every ASM386 program.

## **Lexical Elements**

This section describes the lexical elements of the assembly language, except for its keywords and reserved words.

See also: Keywords and reserved words, Appendix C

## **Character Set**

The assembler character set is a subset of the ASCII character set. Each character in a source file should be one of the following:

Alphanumerics: ABCDEFGHIJKLMNOPQRSTUVWXYZ

abcdefghijklmnopqrstuvwxyz

0123456789

Special Characters: + - \* / ( ) [ ] < > ; ' . "\_: ? @ \$ &

Logical Delimiters: space tab carriage\_return line\_feed

If a program contains any character that is not in the preceding set, the assembler treats the character as a logical space.

Uppercase and lowercase letters are not distinguished from each other except in character strings. For example, xyz and XYZ are interchangeable, but 'xyz' and 'XYZ' are not equivalent character strings.

The special characters and combinations of special characters have particular meanings in a program, as described throughout this manual.

See also: ASCII character set, Appendix D

## **Tokens and Separators**

A token is the smallest meaningful unit of a source program, much as words are the smallest meaningful units of a sentence. A token is one of the following:

- An end of statement

- A delimiter

- An identifier

- A constant

- An assembler keyword or reserved word

A separator that is a logical space or a delimiter must be specified between two adjacent tokens that are identifiers, constants, keywords, and/or reserved words. The most commonly used separator is the space character.

The end of statement token must be specified between two adjacent statements. The most commonly used statement terminator is the carriage\_return/line\_feed character combination.

See also: Constants, Chapter 4

keywords and reserved words, Appendix C

## **Logical Spaces**

Any unbroken sequence of spaces can be used wherever a single space character is valid. Horizontal tabs are also used as token separators. The assembler interprets horizontal tabs as a single logical space. However, tabs are reproduced as multiple space characters in the print (listing) file to maintain the appearance of the source file.

See also: Print file, ASM386 Macro Assembler Operating Instructions

Logical spaces may not be specified within tokens such as identifiers, constants, keywords, or reserved words. The assembler treats any invalid character(s) in the context of a source file as a separator.

## **Delimiters**

Like logical spaces, delimiters mark the end of a token, but each delimiter has a different special meaning. Some examples are commas and colons.

When a delimiter is present, a logical space between two tokens need not be specified. However, extra space or tab characters often make programs easier to read.

Delimiters are described in context throughout this manual.

## **Identifiers**

An identifier is a name for a programmer-defined entity such as a segment, variable, label, or constant. Valid identifiers conform to the following rules:

- The initial character must be a letter (A...Z or a...z) or one of the following special characters:

- ? A question mark (ASCII value: 3FH)

- An at sign (ASCII value: 40H)

- \_ An underscore (ASCII value: 5FH)

- The remaining characters may be letters, digits (0..9), and the preceding special characters. Separators may not be specified within identifiers.

- An identifier may be up to 255 characters in length; it is considered unique only up to 31 characters.

- Every identifier within a program module represents one and only one entity.

A named entity is accessible from anywhere in the module when it is referenced by name. The assembler does not have identifier scope rules that allow you to specify the same name for two distinct entities in different contexts.

## **Continued Statements and Comments**